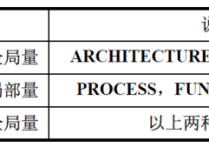

VHDL中的实体 Entity

为了方便显示,文内所有;全部用;显示

ENTITY 实体的格式为:

Entity 实体名 IS 类属参数说明 端口说明 END Entity;

实体名可以是除了VHDL中关键词的其他字母和数字和下划线组成,实体名必须和VHDL源文件的文件夹相同

例如:

ILOVEU Happy123 A_B_C 此类都是合法的实体名

integer entity architecture此类都是非法的实体名

值得注意的是,数字不能作为实体名的开头

例如:

1abc 2k 3jnjkaw 此类都是不合法的实体名

类属参数的格式为:

GENERIC(参数名:类型 := 缺省值; 参数名:类型 := 缺省值);

端口说明的格式为:

PORT(端口名1,端口名2:方向 类型; 端口名3,端口名4:方向 类型);

方向可以为in out buffer

此处的方式都是站在FPGA芯片的角度去看的,比如in,是指从外部输入到in的数据,out是从fpga输出的数据,buffer类似单片机中的BUFF,可读可写

示例

Entity abc is port(a1,a2:in std_logic; cout:out std_logic); End Entity;