SI5394/SI5395/SI5392 上位机实现直接备份、修改、固化、实时配置时钟管理芯片 示例基于Xilinx Alevo U55C/U50/U280 NVM Program

首先说明这玩意非常麻烦,建议直接联系我付费修改。如果你非要自己修改,可能时间成本比联系我还要贵出很多倍。

Firstly, it should be noted that this matter is very troublesome. It is recommended to contact me directly for payment and modification.

If you insist on modifying it yourself, the time cost may be many times more expensive than contacting me.

以下程序是我将U55C的SI5394 OUT0和OUT1的输出由161.1328125MHz修改为156.25Mhz

The following program is for me to modify the output of SI5394 OUT0 and OUT1 of U55C from 161.1328125MHz to 156.25Mhz

本站提供SI5394修改OUT0和OUT1频率的付费服务,支持但不限于156.25Mhz等,能够固化写入,断电后不丢失。

如片内NVM超过写入次数限制,也支持更换硬件芯片,或提供新的黄金工程。

邮寄修改服务,10工作日内完成(可以加急),每个板卡配置费用5000元(含税)。

所有工程及操作教程 23888元(含税)。

支持开票,也支持更多相关功能开发,合作可以邮件联系:chenyu@myfpga.cn

加速卡板载有SI5394,可以输出不同的时钟频率。用于不同的用途,例如万兆以太网等:

1、首先通过I2C扫描得到器件的地址,当然,你也可以直接拆开板卡,万用表测量器件地址的A1和A2

这里直接扫描得到了地址为0x68,源代码可以参考:http://myfpga.cn/index.php/post/460.html

2、设计Verilog程序,实现读写的通信:

3、设计上位机程序,实现页切换、读、写、校验、擦写

结果示例:

4、分析配置,方便进行修改

确认设备型号正确

等级是B

版本是A

I2C地址也确实是0x68 ,不过这个读取有什么用?我知道了地址就能获取地址?

,不过这个读取有什么用?我知道了地址就能获取地址?

设备工作正常

时钟输入也正常

跳过一些状态的显示,不赘述

使用CBPro软件进行配置? 读取到的确实是这样,有啥用?

读取到的确实是这样,有啥用?

状态寄存器掩码为0xDC 对应'b11011100

获取当前的参考时钟方式:

说明使用的是XO,频率

0x22[5] = 1:设备处于Holdover或Free Run模式。

HOLD_HIST_VALID寄存器 (0x053F[1])=0,无历史数据,设备处于Free Run模式。

强制锁定在Free Run模式(无论输入时钟状态)。

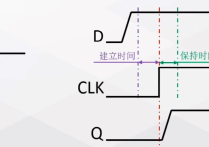

如果希望知道输出频率 ,需要知道N和R

,需要知道N和R

得到N0_NUM=0x2100000000

得到N0_NUM=0x2100000000

得到N0_DEN=0x80000000

得到N0_DEN=0x80000000

N1_NUM=0x1000000000

N1_NUM=0x1000000000

N1_DEN=0xC8000000

N1_DEN=0xC8000000

N2~N3都为0

R0_REG=0,R1_REG=0,R2_REG=1,R3_REG=1,R4_REG~R9_REG均为0

最后是输出格式:

得知几位都是0x09,低3位是001,对应差分标准模式。选择输出为LVPECL/LVDS等差分信号,内部阻抗100Ω

输出电压摆动 0x3E(0011_1110)的[6:4]为011即0x3

共模电压为1110=0xE

当前情况下,FINC和FDEC也能影响分频比例的输出。

当前情况下,FINC和FDEC也能影响分频比例的输出。

后面的过程省略,核心思想就是要弄清楚原理再修改,因为NVM有写入次数限制

最后配置完了之后,向0x00E3写入0xC7即可,此时如果重启后啥也没输出,恭喜你,肯定哪里寄存器改错了。

附上我的成功修改记录: