计算机中的存储结构

存储器的芯片种类:

RAM:随机存储器,可读写,断电后数据无法保存,只能暂存数据。

SRAM:静态随机存储器,在不断电时信息能够一直保持。

DRAM:动态随机存储器,需要定时刷新以维持信息不丢失。

FRAM:铁电随机存储器,速度快,读写功耗极低

ROM:只读存储器,出厂前用掩膜技术写入,常用于存放BIOS和微程序控制。

PROM:可编程ROM,只能够一次写入,需用特殊电子设备进行写入。

EPROM:可擦除的PROM,用紫外线照射15~20分钟可擦去所有信息,可写入多次。

EEPROM:电可擦除ERPOM,可以写入,但速度慢。

FLash:常在U盘使用的种类,可以快速写入

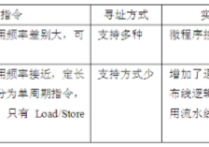

存储器按寻址类型分类,可以分为:

按寻址方式划分,存储器可分为:顺序存储(如:磁带机),直接存储器(如:磁盘、硬盘、光盘),随机存储器(如:内存、U盘)

实际的存储器总是由一片或多片存储器配以控制电路构成的(如图17所示)。其容量为W×B,W是存储单元(wor d,即字)的数量,B表示每个wor d由多少bi t (位)组成。如果某一芯片规格为w×b,则组成W×B的存储器需要用(W/ w)×(B/ b)个芯片。

例:若内存容量为4GB,字长为32,则:A.地址总线和数据总线的宽度都为32

解:

字长是指在同一时间中CPU处理二进制数的位数叫字长。数据总线是用于在计算机中传送数据的总线,它可以把CPU的数据传送到存储器或输入输出接口等其它部件,也可以将其它部件的数据传送到CPU。数据总线的位数是微型计算机的一个重要指标,通常与字长一致,所以字长32也就意味着数据总线的宽度为32。地址总线是传送地址信息的总线,根据地址总线的多少可以确定内存容量的大小,如32位的地址总线可以允许2的32次方的内存容量。

CaChe

由于CPU的寄存器数量有限且容量非常小,尽管寄存器的存读速度极快,但是受到容量的限制。内存的容量很大,但是由于没有集成在CPU上,导致一定会有时延存在,速度有所下降。(其实是胡扯的,主要是成本的因素)基于这两种考虑,人们发明了Cache这样一场缓存的结果,它的速度和容量都介于寄存器和主存之间。

使用Cache改善系统性能的主要依据是程序的局部性原理。通俗地说,就是一段时间内,执行的语句常集中于某个局部。而Cac he正式将访问集中的内容放在速度更快的Cache上,以提高性能。引入Cache后,CPU在需要数据时,先找Cache,如果没有再找内存。如果Cache的访问命中率为h(通常1h就是Cache的失效率),而Cache的访问周期时间是t 1,主存储器的访问周期时间是t 2,则整个系统的平均访存时间就应该是:

从公式可以看出,系统的平均存时间与命中率有着很密切的关系。灵活地应用这个公式,可以计算出所有情况下的平均访存时间。

例如:设某流水线计算机主存的读/ 写时间为100ns ,有一个指令和数据合一的Cache,已知该Cac he的读/ 写时间为l 0ns ,取指令的命中率为98%,取数的命中率为95%。在执行某类程序时,约有1/ 5指令需要存/ 取一个操作数。假设指令流水线在任何时候都不阻塞,则设置Cache后,每条指令的平均访存时间约为多少?其实这是应用该公式的简单数学题:

( 2%×100ns + 98%×10ns ) + 1/ 5×( 5%×100ns+ 95%×10ns ) =14. 7n

Cache的映射类型

映射类型常见的有3种:直接映射,全相联映射,组相联映射

直接映射:是一种多对一的映射关系,但一个主存块只能够复制到Cache的一个特定位置上去。Cache的行号i 和主存的块号j 有函数关系:i =j %m(其中m为Cache总行数)。例如:某Cache容量为16KB(可用14位表示),每的大小为16B(可用4位表示),则说明其可分为1024行(可用10位表示)。则主存地址的最低四位为Cache的行内地址,中间10位为Cache行号。如果内存地址为1234E8F8H的话,那么最后四位就是1000(对应16进制数的最后位),而中间10位,则应从E8F(111010001111)中获取,得到1010001111。

相联映射:将主存中一个块的地址与块的内容一起存于Cache的行中。速度更快,但控制复杂。

组相联映射:是前两种方式的折中方案。它将Cache中的块再分成组。然后通过直接映射方式决定组号,再通过相联映射的方式决定Cache中的块号。

要注意的是,在Cache映射中,主存和Cache存储器将均分成容量相同的块。

例如:容量为64块的Cache采用组相联方式映像,字块大小为128个字,每4块为一组。若主存容量为4096块,且以字编址,那么主存地址应该为多少位?主存区号为多少位?这样的题目,首先根据主存与Cache块的容量需一致,因此内存也是128个字,因此共有128×4096个字,即219( 27+2 12) 个字,因此主存地址需要19位;而内存所需要分为4096/ 64块,即2 6,因此主存区号需要6位。

Cache淘汰算法

当Cache数据已满,并且出现未命中情况时,就是淘汰一些老的数据,更新一些新的数据。而选择淘汰什么数据的方法就是淘汰算法,常见的方法有三种:随机淘汰、先进先出(FIFO)淘汰(淘汰最早调入Cache的数据)、最近最少使用(LRU)淘汰法。其中平均命中率最高的是LRU算法。

Cache存储器的写操作

在使用Cache时,需要保证其数据与主存一致,因此在写Cache时就需要考虑与主存间的同步问题,通常使用以下三种方法:写直达(写Cache时,同时写主存)、写回(写Cache时不马上写主存,而是等其淘汰时回写)、标记法。