自定义Versal BSP创建XSA文件

新建工程:

紧接着添加CIPS

双击,

然后根据你的硬件添加外设,例如我添加SPI的存储器、EMMC和SD卡

这里图片截图有问题,GEM0需要勾选MDIO。

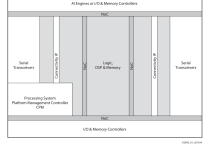

接下来按OK即可,我们现在开始配置NOC

按OK后退出,我们配置这个时钟

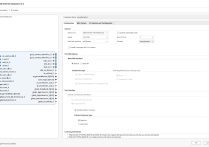

紧接着创建例化模板:

Verilog程序(top.v)

`timescale 1ns / 1ps module top ( CH0_DDR4_0_0_act_n, CH0_DDR4_0_0_adr, CH0_DDR4_0_0_ba, CH0_DDR4_0_0_bg, CH0_DDR4_0_0_ck_c, CH0_DDR4_0_0_ck_t, CH0_DDR4_0_0_cke, CH0_DDR4_0_0_cs_n, CH0_DDR4_0_0_dm_n, CH0_DDR4_0_0_dq, CH0_DDR4_0_0_dqs_c, CH0_DDR4_0_0_dqs_t, CH0_DDR4_0_0_odt, CH0_DDR4_0_0_reset_n, sys_clk0_0_clk_n, sys_clk0_0_clk_p, sys_rst_n_in, PL_LED ); output [0:0] CH0_DDR4_0_0_act_n; output [16:0] CH0_DDR4_0_0_adr; output [1:0] CH0_DDR4_0_0_ba; output [0:0] CH0_DDR4_0_0_bg; output [0:0] CH0_DDR4_0_0_ck_c; output [0:0] CH0_DDR4_0_0_ck_t; output [0:0] CH0_DDR4_0_0_cke; output [0:0] CH0_DDR4_0_0_cs_n; inout [7:0] CH0_DDR4_0_0_dm_n; inout [63:0] CH0_DDR4_0_0_dq; inout [7:0] CH0_DDR4_0_0_dqs_c; inout [7:0] CH0_DDR4_0_0_dqs_t; output [0:0] CH0_DDR4_0_0_odt; output [0:0] CH0_DDR4_0_0_reset_n; input sys_clk0_0_clk_n; input sys_clk0_0_clk_p; input wire sys_rst_n_in; output wire PL_LED; //********************////********************// System Parameter Defines //********************////********************// // Sys clock generate wire sys_clk_200mhz; IBUFDS IBUFDS_inst ( .O (sys_clk_200mhz), .I (sys_clk0_0_clk_p), .IB(sys_clk0_0_clk_n) ); wire sys_rst_n; BUFG bufg_inst ( .I(sys_rst_n_in), // 输入信号 .O(sys_rst_n) // 缓冲后的信号 ); reg [27:0] led_cnt; always @(posedge sys_clk_200mhz or negedge sys_rst_n) begin if (~sys_rst_n) led_cnt <= 28'b0; else led_cnt <= led_cnt + 1; end assign PL_LED = led_cnt[27]; design_1_wrapper design_1_wrapper_1 ( .CH0_DDR4_0_0_act_n(CH0_DDR4_0_0_act_n), .CH0_DDR4_0_0_adr(CH0_DDR4_0_0_adr), .CH0_DDR4_0_0_ba(CH0_DDR4_0_0_ba), .CH0_DDR4_0_0_bg(CH0_DDR4_0_0_bg), .CH0_DDR4_0_0_ck_c(CH0_DDR4_0_0_ck_c), .CH0_DDR4_0_0_ck_t(CH0_DDR4_0_0_ck_t), .CH0_DDR4_0_0_cke(CH0_DDR4_0_0_cke), .CH0_DDR4_0_0_cs_n(CH0_DDR4_0_0_cs_n), .CH0_DDR4_0_0_dm_n(CH0_DDR4_0_0_dm_n), .CH0_DDR4_0_0_dq(CH0_DDR4_0_0_dq), .CH0_DDR4_0_0_dqs_c(CH0_DDR4_0_0_dqs_c), .CH0_DDR4_0_0_dqs_t(CH0_DDR4_0_0_dqs_t), .CH0_DDR4_0_0_odt(CH0_DDR4_0_0_odt), .CH0_DDR4_0_0_reset_n(CH0_DDR4_0_0_reset_n), .sys_clk0_0_clk_n(sys_clk0_0_clk_n), .sys_clk0_0_clk_p(sys_clk0_0_clk_p) ); endmodule

约束文件(top.xdc)

#top

set_property IOSTANDARD LVDS15 [get_ports sys_clk_200mhz_p]

set_property PACKAGE_PIN AB23 [get_ports sys_clk_200mhz_p]

create_clock -period 5.000 -name sys_clk_200mhz [get_ports sys_clk_200mhz_p]

set_property PACKAGE_PIN D10 [get_ports sys_rst_n_in]

set_property IOSTANDARD LVCMOS33 [get_ports sys_rst_n_in]

set_property -dict {PACKAGE_PIN F11 IOSTANDARD LVCMOS33} [get_ports PL_LED]

#DDR4

set_property PACKAGE_PIN AC11 [get_ports {DDR4_act_n[0]}]

set_property PACKAGE_PIN AB12 [get_ports {DDR4_adr[0]}]

set_property PACKAGE_PIN AB17 [get_ports {DDR4_adr[10]}]

set_property PACKAGE_PIN AE13 [get_ports {DDR4_adr[11]}]

set_property PACKAGE_PIN AH12 [get_ports {DDR4_adr[12]}]

set_property PACKAGE_PIN AD15 [get_ports {DDR4_adr[13]}]

set_property PACKAGE_PIN AD21 [get_ports {DDR4_adr[14]}]

set_property PACKAGE_PIN AD17 [get_ports {DDR4_adr[15]}]

set_property PACKAGE_PIN AC13 [get_ports {DDR4_adr[16]}]

set_property PACKAGE_PIN AE22 [get_ports {DDR4_adr[1]}]

set_property PACKAGE_PIN AD22 [get_ports {DDR4_adr[2]}]

set_property PACKAGE_PIN AB15 [get_ports {DDR4_adr[3]}]

set_property PACKAGE_PIN AD12 [get_ports {DDR4_adr[4]}]

set_property PACKAGE_PIN AE17 [get_ports {DDR4_adr[5]}]

set_property PACKAGE_PIN AD16 [get_ports {DDR4_adr[6]}]

set_property PACKAGE_PIN AG11 [get_ports {DDR4_adr[7]}]

set_property PACKAGE_PIN AE14 [get_ports {DDR4_adr[8]}]

set_property PACKAGE_PIN AB14 [get_ports {DDR4_adr[9]}]

set_property PACKAGE_PIN AC16 [get_ports {DDR4_ba[0]}]

set_property PACKAGE_PIN AD11 [get_ports {DDR4_ba[1]}]

set_property PACKAGE_PIN AB18 [get_ports {DDR4_bg[0]}]

set_property PACKAGE_PIN AC19 [get_ports {DDR4_ck_t[0]}]

set_property PACKAGE_PIN AD19 [get_ports {DDR4_ck_c[0]}]

set_property PACKAGE_PIN AB21 [get_ports {DDR4_cke[0]}]

set_property PACKAGE_PIN AC17 [get_ports {DDR4_cs_n[0]}]

set_property PACKAGE_PIN AG12 [get_ports {DDR4_dm_n[0]}]

set_property PACKAGE_PIN AH13 [get_ports {DDR4_dm_n[1]}]

set_property PACKAGE_PIN AE28 [get_ports {DDR4_dm_n[2]}]

set_property PACKAGE_PIN AD24 [get_ports {DDR4_dm_n[3]}]

set_property PACKAGE_PIN V22 [get_ports {DDR4_dm_n[4]}]

set_property PACKAGE_PIN V28 [get_ports {DDR4_dm_n[5]}]

set_property PACKAGE_PIN N28 [get_ports {DDR4_dm_n[6]}]

set_property PACKAGE_PIN U25 [get_ports {DDR4_dm_n[7]}]

set_property PACKAGE_PIN AF14 [get_ports {DDR4_dq[0]}]

set_property PACKAGE_PIN AH18 [get_ports {DDR4_dq[10]}]

set_property PACKAGE_PIN AH20 [get_ports {DDR4_dq[11]}]

set_property PACKAGE_PIN AH14 [get_ports {DDR4_dq[12]}]

set_property PACKAGE_PIN AH22 [get_ports {DDR4_dq[13]}]

set_property PACKAGE_PIN AH15 [get_ports {DDR4_dq[14]}]

set_property PACKAGE_PIN AG22 [get_ports {DDR4_dq[15]}]

set_property PACKAGE_PIN AF26 [get_ports {DDR4_dq[16]}]

set_property PACKAGE_PIN AE26 [get_ports {DDR4_dq[17]}]

set_property PACKAGE_PIN AH27 [get_ports {DDR4_dq[18]}]

set_property PACKAGE_PIN AE27 [get_ports {DDR4_dq[19]}]

set_property PACKAGE_PIN AG18 [get_ports {DDR4_dq[1]}]

set_property PACKAGE_PIN AG27 [get_ports {DDR4_dq[20]}]

set_property PACKAGE_PIN AD26 [get_ports {DDR4_dq[21]}]

set_property PACKAGE_PIN AG26 [get_ports {DDR4_dq[22]}]

set_property PACKAGE_PIN AG28 [get_ports {DDR4_dq[23]}]

set_property PACKAGE_PIN AE24 [get_ports {DDR4_dq[24]}]

set_property PACKAGE_PIN AD25 [get_ports {DDR4_dq[25]}]

set_property PACKAGE_PIN AH24 [get_ports {DDR4_dq[26]}]

set_property PACKAGE_PIN AF25 [get_ports {DDR4_dq[27]}]

set_property PACKAGE_PIN AG23 [get_ports {DDR4_dq[28]}]

set_property PACKAGE_PIN AG25 [get_ports {DDR4_dq[29]}]

set_property PACKAGE_PIN AG15 [get_ports {DDR4_dq[2]}]

set_property PACKAGE_PIN AH23 [get_ports {DDR4_dq[30]}]

set_property PACKAGE_PIN AH25 [get_ports {DDR4_dq[31]}]

set_property PACKAGE_PIN Y22 [get_ports {DDR4_dq[32]}]

set_property PACKAGE_PIN V23 [get_ports {DDR4_dq[33]}]

set_property PACKAGE_PIN Y23 [get_ports {DDR4_dq[34]}]

set_property PACKAGE_PIN W24 [get_ports {DDR4_dq[35]}]

set_property PACKAGE_PIN AA22 [get_ports {DDR4_dq[36]}]

set_property PACKAGE_PIN V24 [get_ports {DDR4_dq[37]}]

set_property PACKAGE_PIN AA21 [get_ports {DDR4_dq[38]}]

set_property PACKAGE_PIN W25 [get_ports {DDR4_dq[39]}]

set_property PACKAGE_PIN AF18 [get_ports {DDR4_dq[3]}]

set_property PACKAGE_PIN V25 [get_ports {DDR4_dq[40]}]

set_property PACKAGE_PIN W27 [get_ports {DDR4_dq[41]}]

set_property PACKAGE_PIN AA28 [get_ports {DDR4_dq[42]}]

set_property PACKAGE_PIN W26 [get_ports {DDR4_dq[43]}]

set_property PACKAGE_PIN Y26 [get_ports {DDR4_dq[44]}]

set_property PACKAGE_PIN AA26 [get_ports {DDR4_dq[45]}]

set_property PACKAGE_PIN AB28 [get_ports {DDR4_dq[46]}]

set_property PACKAGE_PIN AB26 [get_ports {DDR4_dq[47]}]

set_property PACKAGE_PIN P27 [get_ports {DDR4_dq[48]}]

set_property PACKAGE_PIN K27 [get_ports {DDR4_dq[49]}]

set_property PACKAGE_PIN AF13 [get_ports {DDR4_dq[4]}]

set_property PACKAGE_PIN R28 [get_ports {DDR4_dq[50]}]

set_property PACKAGE_PIN L28 [get_ports {DDR4_dq[51]}]

set_property PACKAGE_PIN R27 [get_ports {DDR4_dq[52]}]

set_property PACKAGE_PIN K28 [get_ports {DDR4_dq[53]}]

set_property PACKAGE_PIN T28 [get_ports {DDR4_dq[54]}]

set_property PACKAGE_PIN M27 [get_ports {DDR4_dq[55]}]

set_property PACKAGE_PIN P25 [get_ports {DDR4_dq[56]}]

set_property PACKAGE_PIN L26 [get_ports {DDR4_dq[57]}]

set_property PACKAGE_PIN R26 [get_ports {DDR4_dq[58]}]

set_property PACKAGE_PIN M26 [get_ports {DDR4_dq[59]}]

set_property PACKAGE_PIN AF19 [get_ports {DDR4_dq[5]}]

set_property PACKAGE_PIN T25 [get_ports {DDR4_dq[60]}]

set_property PACKAGE_PIN K26 [get_ports {DDR4_dq[61]}]

set_property PACKAGE_PIN T26 [get_ports {DDR4_dq[62]}]

set_property PACKAGE_PIN J25 [get_ports {DDR4_dq[63]}]

set_property PACKAGE_PIN AG13 [get_ports {DDR4_dq[6]}]

set_property PACKAGE_PIN AE19 [get_ports {DDR4_dq[7]}]

set_property PACKAGE_PIN AH17 [get_ports {DDR4_dq[8]}]

set_property PACKAGE_PIN AG21 [get_ports {DDR4_dq[9]}]

set_property PACKAGE_PIN AG17 [get_ports {DDR4_dqs_t[0]}]

set_property PACKAGE_PIN AG16 [get_ports {DDR4_dqs_c[0]}]

set_property PACKAGE_PIN AG20 [get_ports {DDR4_dqs_t[1]}]

set_property PACKAGE_PIN AH19 [get_ports {DDR4_dqs_c[1]}]

set_property PACKAGE_PIN AC28 [get_ports {DDR4_dqs_t[2]}]

set_property PACKAGE_PIN AD27 [get_ports {DDR4_dqs_c[2]}]

set_property PACKAGE_PIN AF24 [get_ports {DDR4_dqs_t[3]}]

set_property PACKAGE_PIN AF23 [get_ports {DDR4_dqs_c[3]}]

set_property PACKAGE_PIN Y24 [get_ports {DDR4_dqs_t[4]}]

set_property PACKAGE_PIN AA23 [get_ports {DDR4_dqs_c[4]}]

set_property PACKAGE_PIN Y28 [get_ports {DDR4_dqs_t[5]}]

set_property PACKAGE_PIN Y27 [get_ports {DDR4_dqs_c[5]}]

set_property PACKAGE_PIN U27 [get_ports {DDR4_dqs_t[6]}]

set_property PACKAGE_PIN U28 [get_ports {DDR4_dqs_c[6]}]

set_property PACKAGE_PIN P26 [get_ports {DDR4_dqs_t[7]}]

set_property PACKAGE_PIN N27 [get_ports {DDR4_dqs_c[7]}]

set_property PACKAGE_PIN AC22 [get_ports {DDR4_odt[0]}]

set_property PACKAGE_PIN AC24 [get_ports {DDR4_reset_n[0]}]

set_property PACKAGE_PIN AB23 [get_ports {ddr_cref_clk_p[0]}]

然后就可以编译了

生成完成后,点击左上角