全加器(层次化设计)

该篇博客根据上一篇半加器的设计,再结合层次化的设计思想来实现一个全加器!

层次化设计理论部分:

数字电路中根据模块层次的不同有两种基本的结构设计方法:自底向上的设计方法 和 自顶向下的设计方法

自底向上(Bottom-Up)

自底向上的设计是一种传统的设计方法,对设计进行逐次划分的过程是从存在的基本单元出发的,由基本单元构建高层单元,依次向上,直至构建系统,

自上而下(Top-Down)

从系统级开始,把系统分为基本单元,然后再把每个单元划分为下一层次的基本单元,一直这样做下去,直到直接可以用EDA元件库中的原件来实现为止。

混合使用

全加器设计:

全加器模块框图:

层次化设计 -- 用两个半加器组成的全加器模块框图:

代码部分:

选择器代码:在Src文件夹中新建 full_adder.v文件

module full_adder ( input wire in_1, input wire in_2, input wire cin, output wire sum, output wire count ); // 对变量进行重新命名,为了区分来自于哪个半加器 wire h0_sum; wire h0_count; wire h1_count; half_adder half_adder_inst0 ( .in_1 (in_1), .in_2 (in_2), .sum (h0_sum), .count(h0_count) ); half_adder half_adder_inst1 ( .in_1 (cin), .in_2 (h0_sum), .sum (sum), .count(h1_count) ); assign count = (h0_count | h1_count); endmodule

仿真文件代码:在Sim文件夹中新建 tb_full_adder.v文件

`timescale 1ns/1ns

module tb_full_adder();

reg in_1 ;

reg in_2 ;

reg cin ;

wire sum ;

wire count;

initial

begin

in_1 <= 1'b0 ;

in_2 <= 1'b0 ;

cin <= 1'b0 ;

end

initial

begin

$timeformat(-9,0,"ns",6);

$monitor("@time %t:in_1=%b,in_2=%b,cin+%b,sum=%b,count=%b", $time, in_1, in_2, cin, sum, count);

end

always #10 in_1 <= {$random} % 2;

always #10 in_2 <= {$random} % 2;

always #10 cin <= {$random} % 2;

full_adder full_adder_inst

(

.in_1 (in_1),

.in_2 (in_2),

.cin (cin),

.sum (sum),

.count(count)

);

endmodule结果:

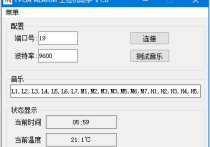

打印的日志正常

波形也正常