“EBAZ4205原理图和PCB免费分享 基于ZYNQ7010” 的相关文章

高速ADC模块开源页面 带Verilog示例程序

暂无...

ALGO C4MB V11引脚参照表(持续更新)

功能:常用引脚CLKPIN_E1LED0PIN_G15LED1PIN_F16LED2PIN_F15LED3PIN_D16KEY1PIN_E15KEY2PIN_E16KEY3PIN_M15KEY4PIN_M16RXDPIN_M2TXDPIN_G1功能:VGA引脚VGA_BLUE[0]PIN_C15VG...

Verilog实现串并转换

项目文件:SIPO.zip//------------------------------------------------------// File Name : SIPO.v// Author &n...

CDC 单脉冲信号处理

代码中的Sys_clk其实是没有用到的,项目文件:cdc_single.zip//------------------------------------------------------// File Name : cdc.v// Autho...

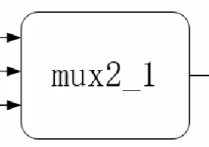

多路选择器

多路选择器:在多路数据传送过程中,能够根据需要将其中任意一路选出来的电路。二选一多路选择器 --- 模块框图in_1:输入信号in_2:输入信号sel:控制选择信号out:输出信号二选一多路选择器 --- 波形图in_1、in_2、sel 的波形是随机的。out 的波形根据控制选通信号而定。当 se...

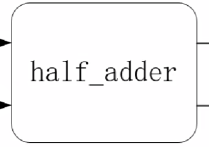

半加器

半加器:两个输入数据位相加,输出一个结果位和进位,没有进位输入的加法器电路。即两个一位二进制数的加法运算电路。半加器 模块框图:sum:结果位count:进位半加器 真值表:半加器 波形图:代码部分:选择器代码:在Src文件夹中新建 half_adder.v文件module half_adder...