半加器

半加器:两个输入数据位相加,输出一个结果位和进位,没有进位输入的加法器电路。即两个一位二进制数的加法运算电路。

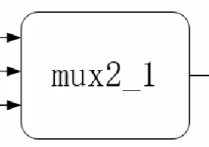

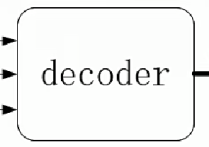

半加器 模块框图:

sum:结果位

count:进位

半加器 真值表:

半加器 波形图:

代码部分:

选择器代码:在Src文件夹中新建 half_adder.v文件

module half_adder

(

input wire in_1 ,

input wire in_2 ,

output wire sum ,

output wire count

);

assign {count,sum} = in_1 + in_2;

endmodule仿真文件代码:在Sim文件夹中新建 tb_half_adder.v 文件

`timescale 1ns/1ns

module tb_half_adder();

reg in_1;

reg in_2;

wire sum;

wire count;

initial

begin

in_1 <= 1'b0;

in_2 <= 1'b0;

end

always #10 in_1 <= {$random} % 2;

always #10 in_2 <= {$random} % 2;

initial

begin

$timeformat(-9,0,"ns",6);

$monitor("@time %t:in_1=%b,in_2=%b,sum=%b,count=%b", $time, in_1, in_2, sum, count);

end

half_adder half_adder_inst

(

.in_1 (in_1),

.in_2 (in_2),

.sum (sum) ,

.count(count)

);

endmodule结果:

打印的日志和真值表中相对应

波形也正常