“EBAZ4205原理图和PCB免费分享 基于ZYNQ7010” 的相关文章

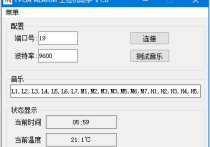

FPGA ALARM FPGA多功能闹钟 完整项目 内含上位机

一、项目简述本项目使用苏州硬禾信息科技有限公司设计的小脚丫FPGA开发板设计了一个完成定时、测温、报警、控制的小项目,并通过上位机显示、下发音乐配置数据。本项目B站介绍:https://www.bilibili.com/video/BV1Vh411k7QV/二、研究进展(一)研究内容:l ...

高速ADC模块开源页面 带Verilog示例程序

暂无...

基础实验十三,DS18B20温度传感器

//==========================================================================// Author : ChanRa1n// Description: Training for Intel FPGA/...

SOC 在线修改设备树和FPGA配置文件 并在线配置FPGA

测试过的平台: 1、DE-10 Cyclone V开发板 ...

Verilog实现时钟分频(奇数分频,偶数分频)二分频 三分频 四分频 五分频

完整工程文件:clkdiv.zip//------------------------------------------------------// File Name : clkdiv.v// Author &nb...