“已上传pdf,从开发到验证的完整手册《FPGA之道》狄超 刘萌著 西安交通大学出版社 pdf” 的相关文章

ALGO C4MB V11引脚参照表(持续更新)

功能:常用引脚CLKPIN_E1LED0PIN_G15LED1PIN_F16LED2PIN_F15LED3PIN_D16KEY1PIN_E15KEY2PIN_E16KEY3PIN_M15KEY4PIN_M16RXDPIN_M2TXDPIN_G1功能:VGA引脚VGA_BLUE[0]PIN_C15VG...

基础实验十三,DS18B20温度传感器

//==========================================================================// Author : ChanRa1n// Description: Training for Intel FPGA/...

CDC 单脉冲信号处理

代码中的Sys_clk其实是没有用到的,项目文件:cdc_single.zip//------------------------------------------------------// File Name : cdc.v// Autho...

点亮LED灯实验

设计流程:设计规划 -> 波形绘制 -> 代码编写 -> 代码编译 -> 逻辑仿真 -> 波形对比 -> 绑定管脚 -> 分析综合布局布线 -> 上板验证新建项目文件夹(led):Doc:放置文档资料(数据手册、波形图、文档、项目日志)Pri:放置工程...

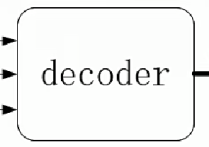

3-8译码器

译码:译码是编码的逆过程,在编码时,每一种二进制的代码,都赋予了特殊的含义,即都表示了一个确定的信号或者对象。把代码状态的特定含义翻译出来的过程叫做译码,实现译码操作的电路称为译码器。译码器:一类多输入多输出的组合逻辑电路器件,其可以分为:变量译码和显示译码两类3-8译码器 模块框图:输出信号定义为...

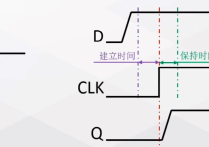

CDC跨时钟域信号处理

保证时序电路的时序要求:建立时间:在有效的时钟沿到来之前,输入端的输入信号需要保持稳定不变的最小时间保持时间:在有效的时钟沿到来之后,输入端的输入信号需要保持稳定不变的最小时间CDC问题1:亚稳态亚稳态原因:亚稳态解决方法:对于单信号来说,使用 Double FF来进行信号同步CDC问题2:数据收敛...