“(手册)LEDA Version 2006.06 User Guide 编码规则检查工具” 的相关文章

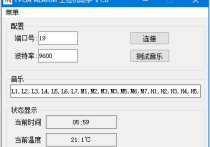

FPGA ALARM FPGA多功能闹钟 完整项目 内含上位机

一、项目简述本项目使用苏州硬禾信息科技有限公司设计的小脚丫FPGA开发板设计了一个完成定时、测温、报警、控制的小项目,并通过上位机显示、下发音乐配置数据。本项目B站介绍:https://www.bilibili.com/video/BV1Vh411k7QV/二、研究进展(一)研究内容:l ...

Intel FPGA初级考试模拟试题 四套含答案

*1.下列对异步信号进行同步的描述错误的是(使用锁存器)。采用保持寄存器加握手信号的方法特殊的具体应用电路结构,根据应用的不同而不同使用锁存器异步 FIFO *2.FPGA 的可编程是主要基于什么结构(查找表(LUT))。查找表(LUT)ROM 可编程PAL 可编程与或阵列可编程解析:FP...

基础实验十三,DS18B20温度传感器

//==========================================================================// Author : ChanRa1n// Description: Training for Intel FPGA/...

Verilog实现时钟分频(奇数分频,偶数分频)二分频 三分频 四分频 五分频

完整工程文件:clkdiv.zip//------------------------------------------------------// File Name : clkdiv.v// Author &nb...

Xilinx FIFO和ILA学习

`timescale 1ns / 1ps//-------------------------------------------------------//Filename ﹕ FIFO_TOP.v//Author ...

Verilog实现串并转换

项目文件:SIPO.zip//------------------------------------------------------// File Name : SIPO.v// Author &n...