读《乌合之众》有感:群体智慧与数字设计的互鉴

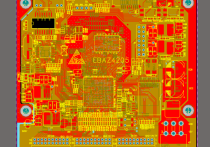

在古斯塔夫·勒庞的《乌合之众:大众心理研究》一书中,他给我们展示了一个细致入微的群体心理世界,揭示了群体行为如何在无数的社会现象中产生深远影响。与此同时,在现代科学技术领域,一个名为FPGA(现场可编程门阵列)的数字设计告诉我们,这种群体智慧同样可以在科技产品中找到体现。

一、勒庞的群体心理学与FPGA的设计原则:体现在拓扑结构与逻辑关联方面

在《乌合之众》一书中,勒庞详细剖析了群体心理的主要特征,包括易于受感情影响,行为与观点的一致性,以及做决策时往往缺乏理性。这些特征在FPGA的设计和工作原理中得到了生动展现。FPGA由大量的可编程逻辑块和可调的互连通道组成,这些元素可以像一个具有集体意识的群体一样,共同完成复杂的数字设计任务。每一个逻辑块就好像群体中的一个个体,虽然单独独立寥寥无几,但是当众多个体联合起来,就能形成一个强大的群体,产生力量与智慧,从而解决复杂的问题。

二、实际运用中的FPGA与集体智慧的映射

FPGA,这样一个充满集体智慧的"数字玩具",能够响应并处理复杂的问题,并在许多领域中发挥着巨大的作用。尤其是在信号处理、图像处理和数据挖掘等领域,FPGA犹如鱼得水,并且发挥出了显著的优势。例如,在图像处理中,FPGA能够并行处理大量像素数据,在并行计算的同时,还能够快速生成处理结果。这种超强的处理能力恰如勒庞所讲的群体智慧一样,众多的个体协同完成同一任务,共享结果,从而完成全局任务。

三、FPGA设计中面临的挑战与群体心理学理论的对照

然而,当FPGA尽享集体智慧带来的红利时,由于群体心理的内在特性,它也不可避免的面临着一些挑战。比如,在设计和部署FPGA时,如何确保每个逻辑块能够协同工作,如何有效地分配和管理资源,如何应对外部环境的变化,这些都是需要我们克服的难题。另一方面,勒庞在《乌合之众》中还提到了群体心理的盲目、易变和不稳定的一面,这些特性也同样存在于FPGA的设计和应用中。为了有效解决这些问题,我们需要通过持续的创新,科学的设计以及使用优化技术。

四、未来展望:以群体心理学研究成果指导FPGA的设计与应用

通过将勒庞的《乌合之众》群体心理学理论与FPGA的工作原理做对比分析,我们能更加深入地理解集体智慧在数字设计中的作用以及扮演的重要角色。FPGA不仅是诠释了数字逻辑技术的新篇章,更是引领了我们看到集体智慧与数字逻辑结合后所可能产生的强大的力量和潜力。对于未来,我们可以通过吸取群体心理学的研究成果,以人性化的角度和思路来优化FPGA的设计,进而促进科技的持续进步。同时,我们也需要对可能带来的问题保持警觉,做到既要挖掘科技的潜力,也要确保其稳定和健康的发展。