Fly-by、Daisy Chain与T-topology对比

*以下内容的版权归MyFPGA.cn所有,仅用于非营利性的学习和教育目的,未经允许不得私自进行转载、引用或商业用途。

在高速数字电路设计中,信号完整性(SI)和时序控制是核心挑战。不同的布线拓扑结构直接影响信号质量、抗干扰能力和系统稳定性。本文将对三种主流高速信号布线拓扑——Fly-by、Daisy Chain(菊花链)和T-topology进行全面对比,分析其原理、优缺点及适用场景。

一、Fly-by拓扑结构

1. 定义与结构特点

Fly-by拓扑通过主控芯片(如CPU或FPGA)依次连接多个负载(如DRAM颗粒),信号从主控出发,依次经过各负载后,在末端通过端接电阻(Termination)完成阻抗匹配。典型应用包括DDR3/4/5内存布线。

结构示意图:

主控 → 负载1 → 负载2 → ... → 负载N → 端接电阻

Fly-by是一种特殊的菊花链,必须要终端电阻(40-60Ω),吸收末端反射波,保证信号干净。

2. 优点

高频适应性:末端端接有效抑制反射,支持GHz级高频信号。

时序易控制:通过调整走线长度补偿各负载的时序差异(Write Leveling技术)。

信号完整性好:Stub(分支线)长度极短,减少振铃和过冲。

支持多负载:适用于多颗粒内存模块(如8片DDR4颗粒)。

3. 缺点

布线复杂度高:需严格控制走线长度和阻抗一致性。

端接电阻要求:末端端接可能增加PCB面积和成本。

负载顺序敏感:负载物理位置影响信号路径,需按顺序布局。

4. 典型应用

DDR3/4/5内存模块

高速SerDes链路(如PCIe Gen4以上)

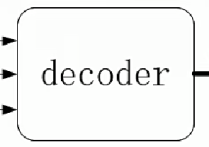

二、Daisy Chain(菊花链)拓扑

1. 定义与结构特点

Daisy Chain将多个负载串联成链状,信号从主控出发依次经过各负载,最后端接。常见于低速外设或地址/控制信号布线。

结构示意图:

主控 → 负载1 → 负载2 → ... → 负载N → 端接电阻

2. 优点

布线简单:单一路径连接所有负载,减少走线分支。

节省空间:无需复杂分支,适合高密度PCB设计。

低频率适用性:在100MHz以下场景表现良好。

3. 缺点

信号反射严重:长链导致阻抗不连续,易产生振铃(Ringing)。

时序难以控制:远端负载信号延迟较大。

负载数量受限:一般不超过4个,否则信号质量急剧下降。

4. 改进方案

源端端接:在主控端串联电阻(典型值22-33Ω),抑制反射。

缩短链长:优先布局靠近主控的负载。

5. 典型应用

SPI、I2C总线外设(如传感器阵列)

低速控制信号(如GPIO扩展)

低速信号终端电阻可接可不接,看心情。

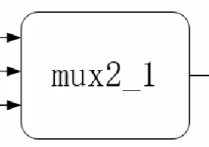

三、T-topology(T型拓扑)

1. 定义与结构特点

T-topology从主控分出对称的两条或多条分支,每条分支连接多个负载。传统DDR2内存和部分PCIe设计曾采用此结构。

结构示意图:

主控 / \ 分支1 分支2 ↓ ↓ 负载1 负载2

2. 优点

对称布局:分支长度相等,便于时序对齐。

多分支支持:适合主控两侧布局的PCB(如双通道内存)。

中频适用:在200-800MHz范围内表现稳定。

3. 缺点

阻抗突变:分支节点导致阻抗不连续,反射问题突出。

高频限制:超过1GHz时信号完整性急剧恶化。

布线难度高:需保证各分支严格等长,增加设计时间。

4. 典型应用

早期DDR2内存设计

双通道PCIe扩展卡

四、三种拓扑对比总结

| 对比项 | Fly-by | Daisy Chain | T-topology |

|---|---|---|---|

| 适用频率 | >1GHz | <100MHz | 200MHz-800MHz |

| 信号完整性 | 最优(末端端接) | 较差(需源端端接) | 中等(分支反射) |

| 布线复杂度 | 高(需长度匹配) | 低(单路径) | 中(多分支等长) |

| 负载数量 | 多(4-8个) | 少(2-4个) | 中(2-4个) |

| 时序控制 | 精确(Write Leveling) | 困难 | 中等 |

| PCB面积占用 | 较大(端接电阻) | 最小 | 中等 |

五、选型建议

超高频场景(>1GHz):优先选择Fly-by拓扑(如DDR4/5、PCIe Gen5)。

低成本/低速设计:采用Daisy Chain并增加源端端接(如传感器网络)。

对称布局需求:考虑T-topology但需限制频率(如双通道ADC阵列)。

混合使用:同一PCB中,高速信号用Fly-by,控制信号用Daisy Chain。

六、设计注意事项

端接策略:

Fly-by必须使用末端端接(通常为40-60Ω电阻)。

Daisy Chain建议源端端接+末端弱上拉。

Stub长度控制:

Fly-by的Stub应<50mil(1.27mm)。

T-topology分支长度差异需<5%。

仿真验证:

使用SI工具(如HyperLynx、ADS)进行眼图和TDR分析。

检查过孔阻抗(建议Via阻抗偏差<±10%)。