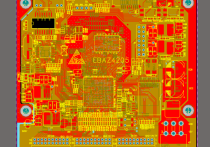

B50612D RGMII Verilog程序设计 UDP Demo

B50612D Datesheet: B50612D-datasheet.pdf

B50612D-datasheet.pdf

对于B50612D这个芯片来说,使用的是RGMII接口,时钟频率和GMII一致,都是1000/8=125Mhz,但是省去了一半的引脚,所以在时钟的双边沿进行传输。

一、操作流程

芯片提供了一个低有效的复位接口,在上电后需要保持复位有效至少10ms+20us才能正常操作,这里我延时15ms。

正常通信时有两种模式,一种是正常模式

另外一种是不正常模式(延时模式)

可以很明显的看出来,正常模式的收发时钟上下边沿均代表对应数据的改变。PHY芯片在发送(TX)和接收(RX)路径均内部延迟时钟约1.5–2ns,使时钟边沿位于数据窗口中央,确保采样稳定。

发送接收默认均为延时模式,所以我们在设计Verilog程序的时候,需要对复位和时钟模式进行修改即可。

我的XDC相关部分如下:

###############################################################################

# Ethernet PHY 0 (U5) -- eth0

###############################################################################

create_clock -period 8.000 -name eth0_rxc [get_ports eth0_rxc]

set_property CLOCK_DEDICATED_ROUTE FALSE [get_nets eth0_rxc]

set_property -dict {PACKAGE_PIN H4 IOSTANDARD LVCMOS33} [get_ports eth0_rxc]

set_property -dict {PACKAGE_PIN E3 IOSTANDARD LVCMOS33} [get_ports {eth0_rxd[0]}]

set_property -dict {PACKAGE_PIN E2 IOSTANDARD LVCMOS33} [get_ports {eth0_rxd[1]}]

set_property -dict {PACKAGE_PIN E1 IOSTANDARD LVCMOS33} [get_ports {eth0_rxd[2]}]

set_property -dict {PACKAGE_PIN F3 IOSTANDARD LVCMOS33} [get_ports {eth0_rxd[3]}]

set_property -dict {PACKAGE_PIN F1 IOSTANDARD LVCMOS33} [get_ports eth0_rx_ctl]

set_property -dict {PACKAGE_PIN A1 IOSTANDARD LVCMOS33} [get_ports eth0_txc]

set_property -dict {PACKAGE_PIN B2 IOSTANDARD LVCMOS33} [get_ports {eth0_txd[0]}]

set_property -dict {PACKAGE_PIN B1 IOSTANDARD LVCMOS33} [get_ports {eth0_txd[1]}]

set_property -dict {PACKAGE_PIN C2 IOSTANDARD LVCMOS33} [get_ports {eth0_txd[2]}]

set_property -dict {PACKAGE_PIN D2 IOSTANDARD LVCMOS33} [get_ports {eth0_txd[3]}]

set_property -dict {PACKAGE_PIN D1 IOSTANDARD LVCMOS33} [get_ports eth0_tx_ctl]

set_property -dict {PACKAGE_PIN H2 IOSTANDARD LVCMOS33} [get_ports eth_rst_n]

###############################################################################

# Ethernet PHY 1 (U9) -- eth1

###############################################################################

create_clock -period 8.000 -name eth1_rxc [get_ports eth1_rxc]

set_property CLOCK_DEDICATED_ROUTE FALSE [get_nets eth1_rxc]

set_property -dict {PACKAGE_PIN L3 IOSTANDARD LVCMOS33} [get_ports eth1_rxc]

set_property -dict {PACKAGE_PIN N2 IOSTANDARD LVCMOS33} [get_ports {eth1_rxd[0]}]

set_property -dict {PACKAGE_PIN N3 IOSTANDARD LVCMOS33} [get_ports {eth1_rxd[1]}]

set_property -dict {PACKAGE_PIN P1 IOSTANDARD LVCMOS33} [get_ports {eth1_rxd[2]}]

set_property -dict {PACKAGE_PIN P2 IOSTANDARD LVCMOS33} [get_ports {eth1_rxd[3]}]

set_property -dict {PACKAGE_PIN R1 IOSTANDARD LVCMOS33} [get_ports eth1_rx_ctl]

set_property -dict {PACKAGE_PIN M6 IOSTANDARD LVCMOS33} [get_ports eth1_txc]

set_property -dict {PACKAGE_PIN M5 IOSTANDARD LVCMOS33} [get_ports {eth1_txd[0]}]

set_property -dict {PACKAGE_PIN M2 IOSTANDARD LVCMOS33} [get_ports {eth1_txd[1]}]

set_property -dict {PACKAGE_PIN N4 IOSTANDARD LVCMOS33} [get_ports {eth1_txd[2]}]

set_property -dict {PACKAGE_PIN P4 IOSTANDARD LVCMOS33} [get_ports {eth1_txd[3]}]

set_property -dict {PACKAGE_PIN N5 IOSTANDARD LVCMOS33} [get_ports eth1_tx_ctl]

set_false_path -from [get_ports sys_rst_n] -to [get_ports eth_rst_n]

set_false_path -from [get_ports eth_rst_n] -to [all_outputs]

create_clock -period 8.000 -name eth0_rxc [get_ports eth0_rxc]

set_input_delay -clock eth0_rxc -max -1.2 [get_ports {eth0_rxd[*]}]

set_input_delay -clock eth0_rxc -min -2.8 [get_ports {eth0_rxd[*]}]

set_input_delay -clock eth0_rxc -max -1.2 [get_ports eth0_rx_ctl]

set_input_delay -clock eth0_rxc -min -2.8 [get_ports eth0_rx_ctl]

create_clock -period 8.000 -name eth0_txc [get_ports eth0_txc]

set_output_delay -clock eth0_txc -max -0.9 [get_ports {eth0_txd[*]}]

set_output_delay -clock eth0_txc -min -2.9 [get_ports {eth0_txd[*]}]

set_output_delay -clock eth0_txc -max -0.91.5 [get_ports eth0_tx_ctl]

set_output_delay -clock eth0_txc -min -2.90.5 [get_ports eth0_tx_ctl]

set_property CLOCK_DEDICATED_ROUTE FALSE [get_nets eth0_rxc]

set_property CLOCK_DEDICATED_ROUTE FALSE [get_nets eth0_txc]

set_property -dict {PACKAGE_PIN G1 IOSTANDARD LVCMOS33} [get_ports eth0_mdc]

set_property -dict {PACKAGE_PIN G2 IOSTANDARD LVCMOS33} [get_ports eth0_mdio]

create_clock -period 80.000 -name eth0_mdc [get_ports eth0_mdc]

set_input_delay -clock eth0_mdc -max 10 [get_ports eth0_mdio]

set_input_delay -clock eth0_mdc -min 0 [get_ports eth0_mdio]

set_output_delay -clock eth0_mdc -max 10 [get_ports eth0_mdio]

set_output_delay -clock eth0_mdc -min 0 [get_ports eth0_mdio]

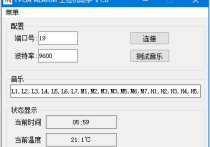

set_clock_groups -asynchronous -group [get_clocks sys_clk_25mhz] -group [get_clocks eth0_rxc] -group [get_clocks eth0_txc]编译上电测试:

收发均正常,收工!