“(手册)SpyGlass® CDC Customer Training Release 5.1.0” 的相关文章

Intel FPGA初级考试模拟试题 四套含答案

*1.下列对异步信号进行同步的描述错误的是(使用锁存器)。采用保持寄存器加握手信号的方法特殊的具体应用电路结构,根据应用的不同而不同使用锁存器异步 FIFO *2.FPGA 的可编程是主要基于什么结构(查找表(LUT))。查找表(LUT)ROM 可编程PAL 可编程与或阵列可编程解析:FP...

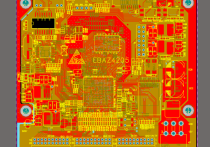

EBAZ4205原理图和PCB免费分享 基于ZYNQ7010

ebit.pdfebit.PcbDoc...

ALGO C4MB V11引脚参照表(持续更新)

功能:常用引脚CLKPIN_E1LED0PIN_G15LED1PIN_F16LED2PIN_F15LED3PIN_D16KEY1PIN_E15KEY2PIN_E16KEY3PIN_M15KEY4PIN_M16RXDPIN_M2TXDPIN_G1功能:VGA引脚VGA_BLUE[0]PIN_C15VG...

Verilog实现时钟分频(奇数分频,偶数分频)二分频 三分频 四分频 五分频

完整工程文件:clkdiv.zip//------------------------------------------------------// File Name : clkdiv.v// Author &nb...

Xilinx FIFO和ILA学习

`timescale 1ns / 1ps//-------------------------------------------------------//Filename ﹕ FIFO_TOP.v//Author ...

Verilog实现串并转换

项目文件:SIPO.zip//------------------------------------------------------// File Name : SIPO.v// Author &n...